#### ABSTRACT

# JANUS: A REALTIME TIMESHARING COMPUTER SYSTEM FOR USE IN NUCLEAR PHYSICS EXPERIMENTS

A By

### John Oscar Kopf

A computer program called JANUS has been developed for use on a Seientific Data Systems Sigma Seven computer. JANUS is a computer operating system, designed to permit many different users to share the resources of the computer, such that each user is apparently in sole control of the machine. These resources include the time available for operation, the program and data storage available, and communication links with the world external to the computer.

A comparison of the means and mechanisms of resource management provided by various computer operating systems, including JANUS, is presented. Descriptions of inadequacies, both in hardware and in operating systems, are given, with suggestions on possible improvements in future implementations. In those cases where it has been possible to measure various parameters under JANUS operation, the measurement and a comment on its significance is provided. Reference manuals for JANUS and various control monitor tasks are appended, as well as thoughts on the possible implementation of other desireable processes.

A novel method has been developed to handle realtime processes.

The computer may be used to simultaneously control devices, acquire data, and perform analysis and computation. Any process may be started or stopped at random, irrespective of the other usage of the machine. The flexibility introduced into the use of the computer, compared with conventional realtime systems, is impressive, since, if necessary, all

of the resources of the computer may be directed toward any goal, using a single operating system, without the overhead normally associated with such systems.

This is accomplished by providing within the resident monitor only those primitive functions dealing with resources common to all usage. Higher level functions, such as Input/Output, are provided by independent timeshared tasks. These tasks, with the features normally associated with conventional monitors, provide those functions necessary and sufficient to the operation of a specific set of problems.

# JANUS: A REALTIME TIMESHARING COMPUTER SYSTEM FOR USE IN NUCLEAR PHYSICS EXPERIMENTS

By

John Oscar Kopf

## A THESIS

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

Department of Physics

Dedication:

For my wife Peggy

Who minded the kids.

#### ACKNOWLEDGMENTS

I wish to acknowledge my indebtedness to all the people who helped make JANUS, and this thesis, possible.

First and foremost, I am grateful to my advisor, Professor

Asron Galonsky, for his patience and encouragement, and for allowing

me a free hand in the design and implementation of JANUS.

Secondly, I acknowledge the great assistance of Mr. Phillip

Plauger, whose familiarity with other computers and computer operating systems, and whose willingness to engage in many all-night bull

sessions, helped immeasurably in the design of JANUS, to say nothing

of the fact that the original idea to write the timesharing system

which became JANUS was his.

Third, I wish to thank Richard Au, Douglas Bayer, Carolee and William Merritt, Francis Schiffer, and Laurence Wilbur for their programming assistance in coding tasks, libraries, symbionts, and other parts of JANUS, as well as their aid in finding and correcting errors in JANUS. In leaving, I feel that JANUS is in good hands, and will continue to grow in use.

Fourth, I acknowledge the assistance of Mr. Lester Hanson and Mr. Donald Freedman, who, as on-site engineering representatives of SDS, were instrumental in quickly verifying, redesigning, and changing those design errors which are always present in a new computer. Without these changes, the Sigma ? would be incapable of running JANUS. I

also wish to cite SDS, which delivered an operating system with the computer, without which it would have been impossible to even begin to start JANUS.

Fifth, I wish to thank Mr. Robert Belgard, who drafted most of the figures presented, and Mrs. Susan West, who typed the thesis.

I also wish to thank all of the other people at the M.S.U. Cyclotron Laboratory, too numerous to name, who in one way or another helped with JANUS. My thanks especially to those people whose constant insistance that I justify JANUS, thereby forced me to re-evaluate the design of JANUS at all stages, and caused me to formulate a flexible and self-consistent system.

Finally, I wish to acknowledge the financial assistance contributed by the National Science Foundation and by Michigan State University.

# TABLE OF CONTENTS

| Cha | pter                               | Page |

|-----|------------------------------------|------|

|     | Table of Contents                  | •    |

|     | List of Figures                    | vii  |

| 1.  | Introduction                       | 1    |

| 2.  | The Use of Core Memory             | 12   |

| 3.  | Bulk Storage                       | 28   |

| 4.  | Scheduling of Time                 | 35   |

| 5.  | Design Goals of JANUS              | 42   |

| 6.  | Unique Features of JANUS           | 174  |

| 7.  | The Target Computer                | 46   |

| 8.  | Structure of JANUS                 | 52   |

| 9•  | Address Spaces                     | 60   |

| 10. | JAMUS and HPM: A Comparison        | 66   |

| 11. | Measurements                       | 72   |

| 12. | Conclusions                        | 76   |

|     | Bibliography                       | 80   |

|     | Appendix A. Glossary of Terms      | 82   |

|     | Appendix B. JAMUS Reference Manual | 86   |

|     | 1. Resident Tables and Lists       | 86   |

|     | 2. Resident Routines               | 98   |

|     | 3. Demand Paging                   | 105  |

|     | 4. Program Optimisation            | 115  |

|     | 5. Signals and the Message Center  | 117  |

| 6.               | Time        | keer | ing    | •     | •     | • ,  | • .   | •    | •     | •    | . •  | •    | • | 119 |

|------------------|-------------|------|--------|-------|-------|------|-------|------|-------|------|------|------|---|-----|

| 7.               | Uniq        | ue I | gesoni | ces   |       | •    | •     | •    | •     | •    | •    | •    | • | 122 |

| 8.               | Pref        | ice  | and    | the   | Cons  | ole  | Tele  | type | •     | •    | •    | •    | • | 127 |

| 9.               | Disk        | Pi]  | .es    | •     |       | •    | •     | •    | •     | •    | • ·  | •    | • | 131 |

| 10.              | <b>Symb</b> | iont |        | •     | •     | •    | •     | •    | •     | •    | •    | •    | • | 134 |

| 11.              | Cont        | rol  | Comme  | and s | and   | the  | Ampe  | rsca | ner   | Task | •    | •    | • | 136 |

| 12.              | The         | Hou  | ekeer  | er I  | 'ask  | •    | .•    | •    | •     | •    | •    | •    | • | 138 |

| <b>A</b> ppendi: | k C.        | The  | JAN    | JS Be | sic/  | File | Cor   | trol | . Mor | itor | 78   | •    | • | 141 |

| <b>A</b> ppendi: | k D.        | Not  | es or  | ı Cyc | clotr | on C | onti  | ol I | mple  | ment | atio | n    | • | 146 |

| Appendi          | ĸ E.        | Not  | es or  | ı Cor | vent  | ions | al Te | rmin | al I  | mple | ment | atio | a |     |

| linda            | ar JA       | MIS  |        | _     |       |      |       |      |       |      |      |      |   | 151 |

# LIST OF FIGURES

| Fig | ure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

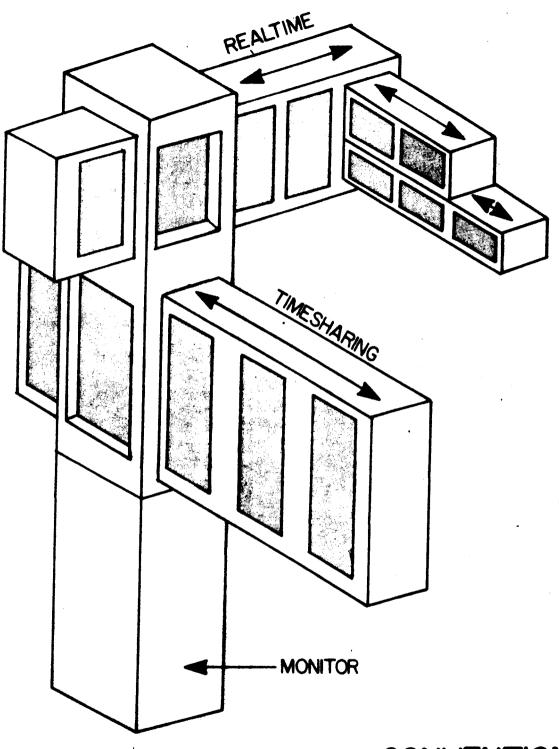

| 1.  | Memory allocation under a foreground-background scheme of timesharing. The vertical column represents core memory. The monitor is used to provide all control functions. The area of core devoted to background timesharing is successively occupied by a number of processes, all limited to the size of the background area. The realtime foreground area may be occupied by any one of a set of processes, (or divided so that it may be used by more than one processes), but any realtime process generally locks out all other realtime processes. | . 7  |

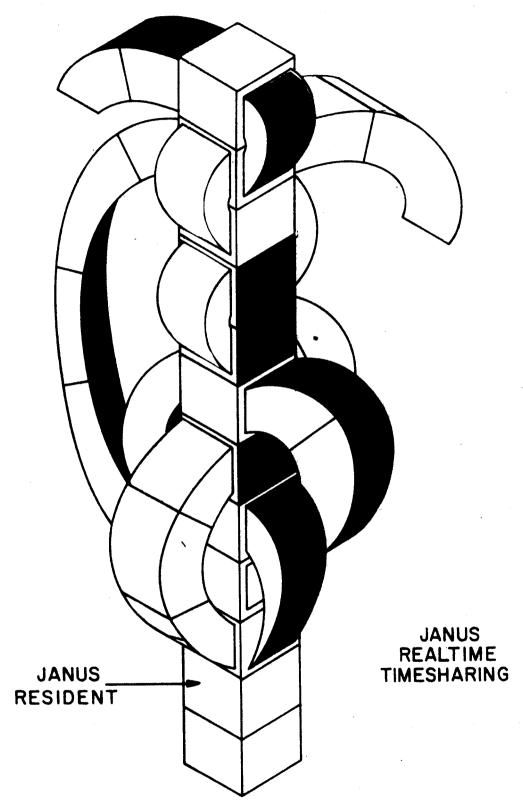

| 2.  | Memory allocation under JANUS. As in Figure 1, the column represents core memory, with JANUS at the bottom. Two tasks are shown, with the independent task address spaces twining through memory. Not all pages of a task need be in core at one time. The darkened pages of core are dedicated to realtime processes specific to the task which has the page                                                                                                                                                                                            | 11   |

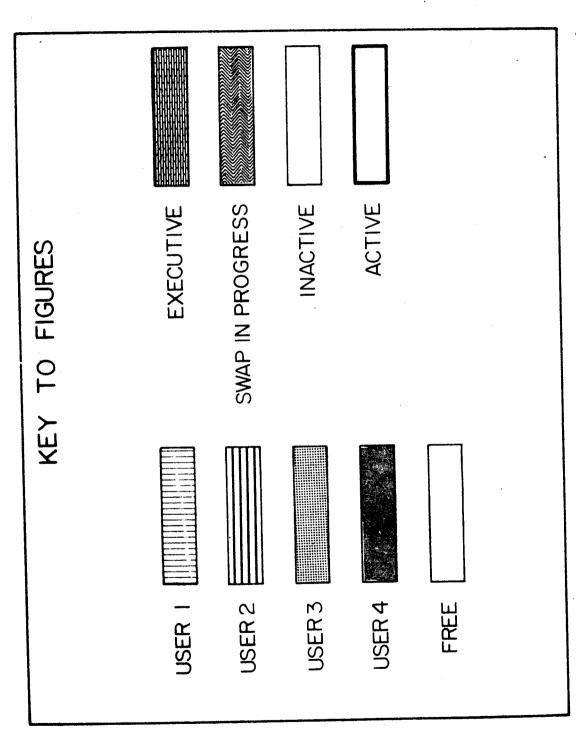

| 3.  | Key to subsequent figures. (Note the use of the word active, which in this context refers to a task executing a timeslice.)                                                                                                                                                                                                                                                                                                                                                                                                                              | 13   |

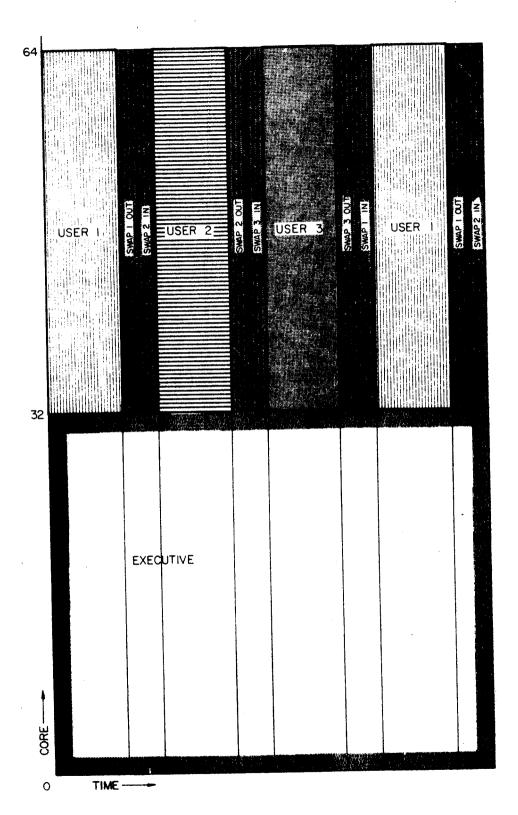

| 4.  | Memory allocationproject MAC. User execution alternates with awapping (the process where the program is transferred to or from memory)                                                                                                                                                                                                                                                                                                                                                                                                                   | 15   |

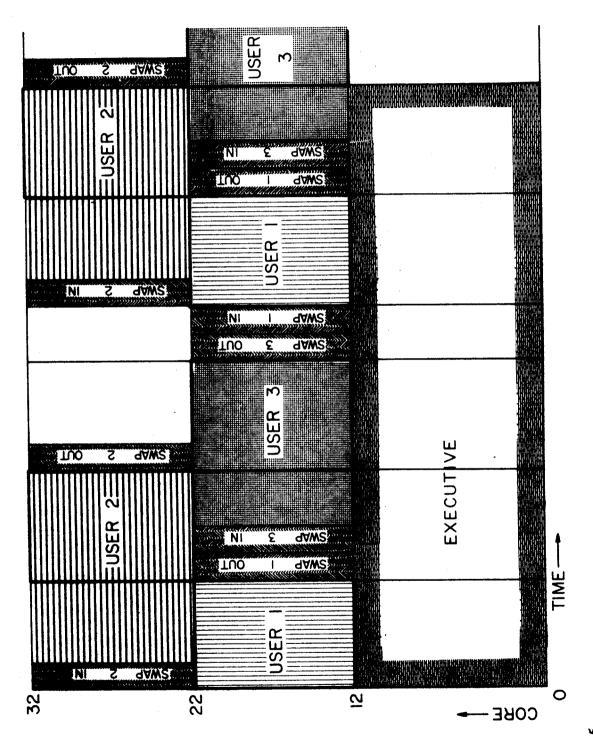

| 5•  | Memory allocation—Dartmouth project. A new program is swapped into core memory while the current program is executing. However, an imbalance in the number of jobs assigned to high and low storage causes a delay at the end of the third timeslice, as there is nothing to do but wait between USER 3 and USER 1                                                                                                                                                                                                                                       | 19   |

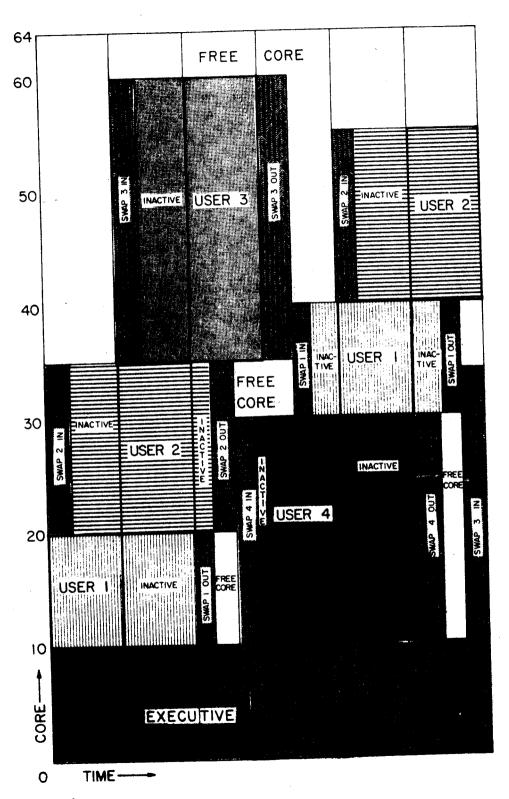

| 6.  | Memory allocation—PDP-6 computer. Swapping occurs concurrently with execution, but the efficiency is higher than in Figure 5, as no limitation is imposed by the use of specific areas. Note that a significant part of memory is rarely or never used                                                                                                                                                                                                                                                                                                   | 22   |

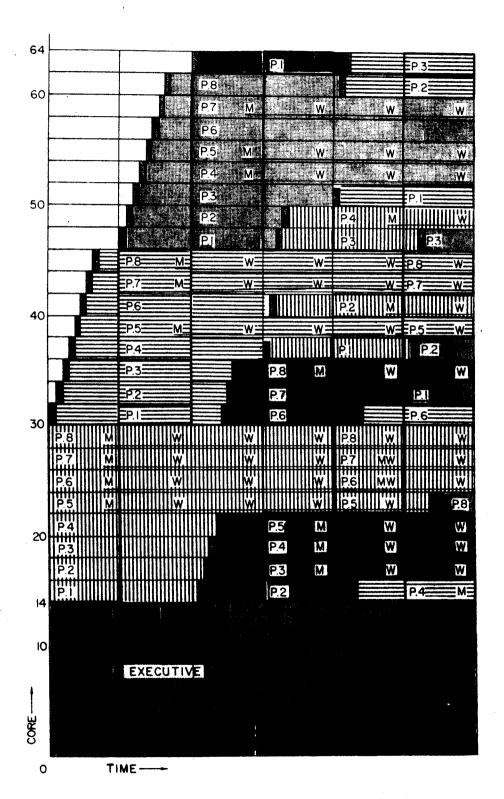

| 7.  | Memory allocationproject GENIE. Problems are initially brought into free core. When no more core                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|     | not currently in use and are identical to the copy on the disk (unmodified), to be overwritten by new pages. The resultant fragmentation of jobs is offset by the use of a memory map. Not until the sixth timeslice is it necessary to write a page out to the disk (TASK 1, Page 5). This scheme is also used in JAMUS. (The P numbers are pages within each user's address space. M signifies that the page is modified, W indicates that it must be written onto the disk.) |   | 24         |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|

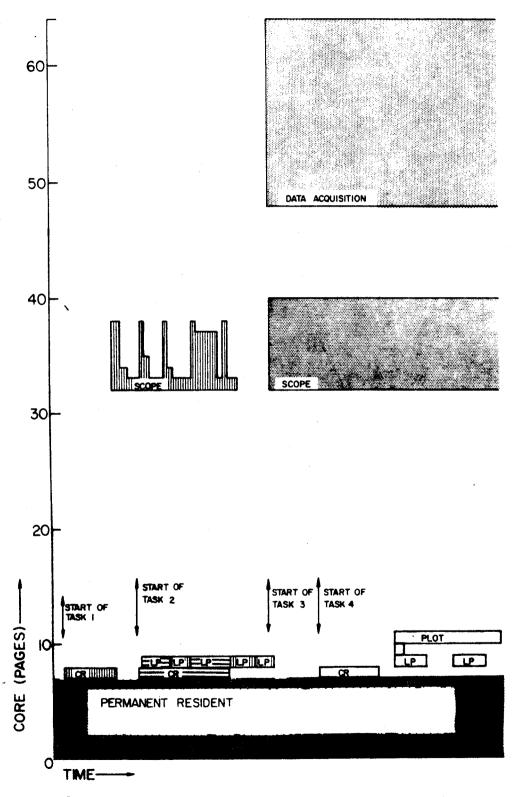

| 8.  | Gross memory allocation under JANUS, showing real-<br>time processes. Using a large time scale, all short-<br>term details of memory usage are omitted. Shown<br>instead are areas dedicated for realtime processes.<br>The blank area is available for swapping. The ac-<br>tivation of four tasks is shown, each of which im-                                                                                                                                                 | • | ag v       |

|     | mediately initiates a realtime data input process.  These tasks, in order of appearance, might be MOIRAE, JBCM, DATA TAKER, and JFCM. Note the in- terleaving of lineprinter output of tasks 1 and 2.  The variable size scope display is a measure of the amount of realtime buffer area required as a display is expanded to show relationships instead of detail.                                                                                                            | • | 27         |

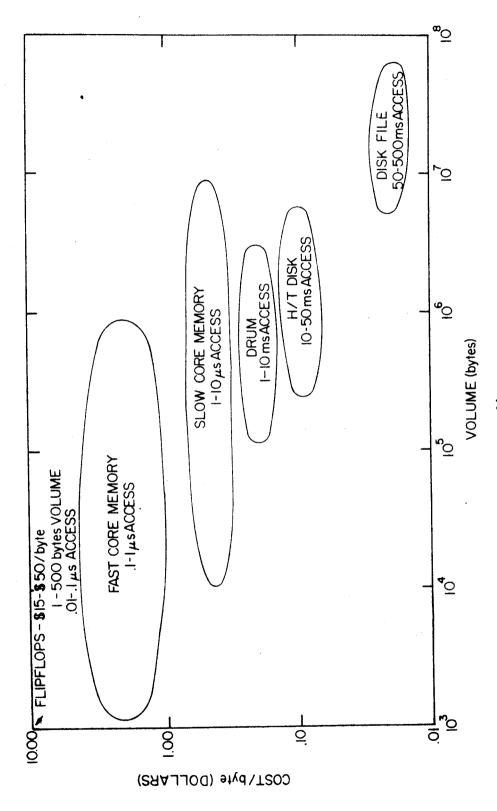

| 9.  | Characteristics of various bulk storage media                                                                                                                                                                                                                                                                                                                                                                                                                                   | • | 29         |

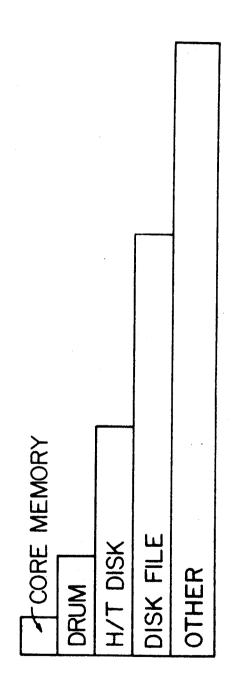

| 10. | Linear bulk storage structure. (Used by CDC 6600 (extended core storage) to hold programs and non-executable I/O buffers.)                                                                                                                                                                                                                                                                                                                                                      | • | 31         |

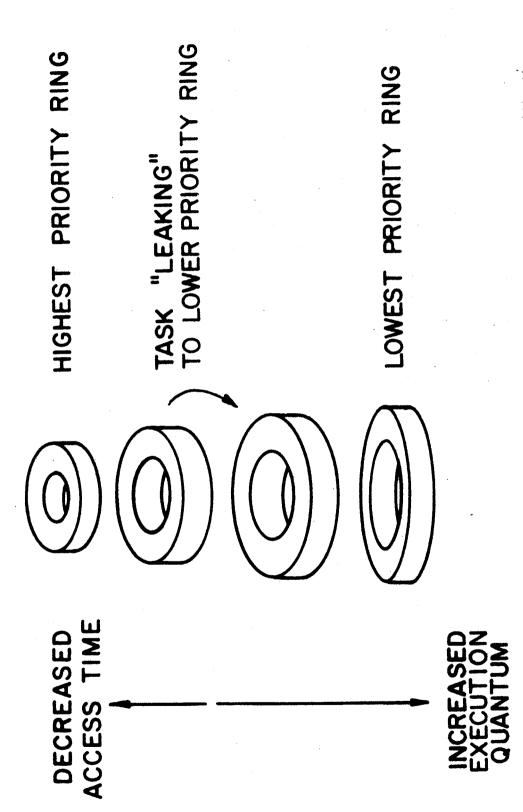

| 11. | Hierarchical storage structure. Access time decreases with height. Each storage medium has an independent address space                                                                                                                                                                                                                                                                                                                                                         |   | 31         |

| 12. | Hybrid storage structure                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • | 3 <b>3</b> |

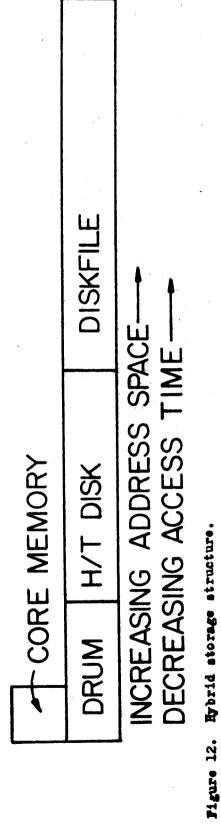

| 13. | Priority scheduling. A task in a high priority ring will be accessed more rapidly than one on a lower ring                                                                                                                                                                                                                                                                                                                                                                      | • | 38         |

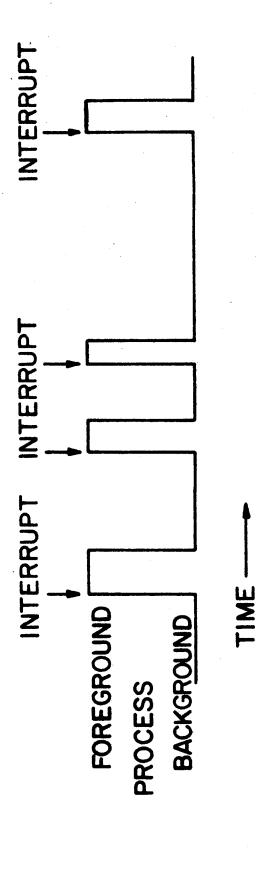

| L4. | "Timesharing" by interrupts. Execution alternates<br>between the background (lower) and foreground (upper)<br>line, on the basis of interrupts. While a simple<br>case is shown, interrupts need not all belong to the<br>same foreground process                                                                                                                                                                                                                               | • | 40         |

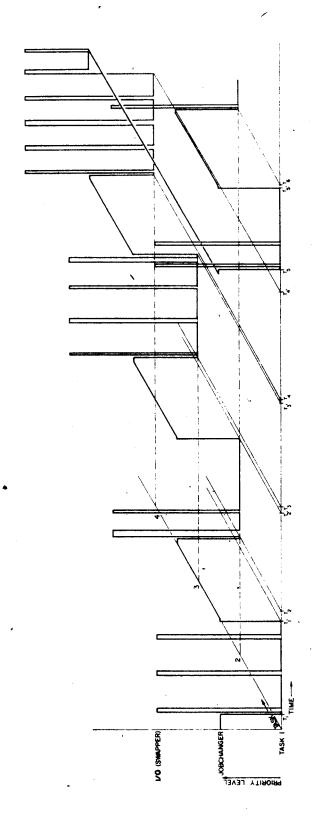

| 15. | Typical world line of JAMUS operation. The path of operation (heavy line) proceeds through a task 1 from T <sub>j</sub> to T <sub>j</sub> , interrupted by the swapper. At each T <sup>i</sup> , it passes to the jobehanger, which performs operations (interruptable by the swapper, as between T <sub>k</sub> , and T <sub>j</sub> ), and returns to the next task in the ring. Each interrupt by the Swapper is used to initiate a                                          |   |            |

|     | new RAD operation, or finish an old operation.  These RAD operations are used to ready the next task.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • | 53  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

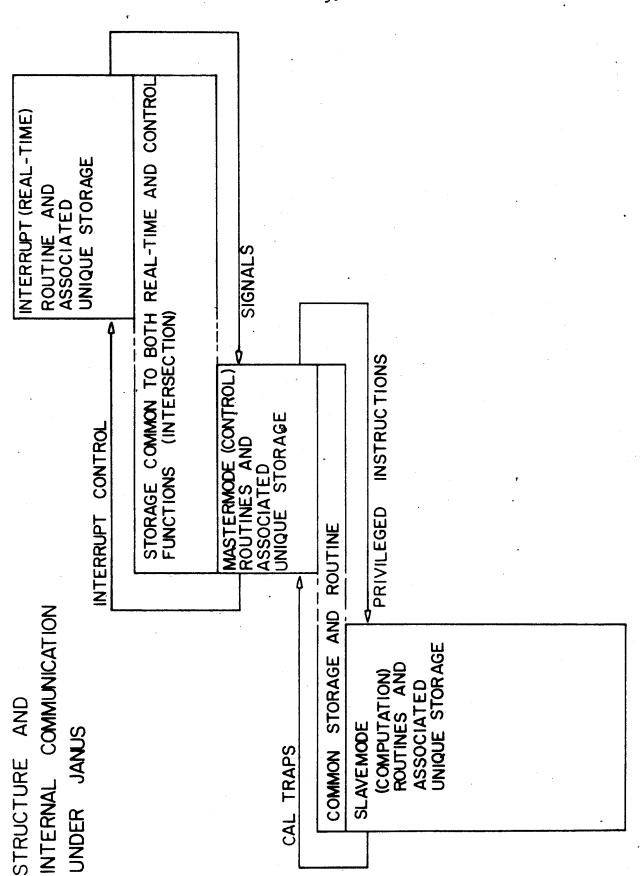

| 16. | JAMUS form of control structure. Operations are divided into three parts; mapped slave, mapped master, and unmapped realtime. Paths of communication between the three parts are shown by arrows.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • | 56  |

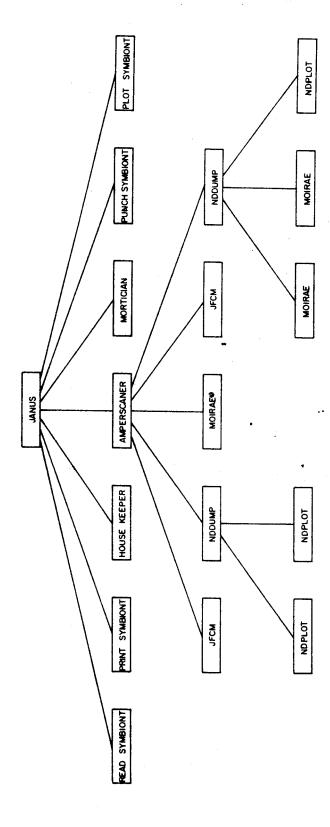

| 17. | Tree structure of tasks. The first rank of tasks below JANUS are the system tasks. One of these (the Ampersoner), can start subtasks, which may start subtasks of their own. These subtasks may be identical copies of tasks which may be started by the Ampersoner, or they may be unique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • | 57  |

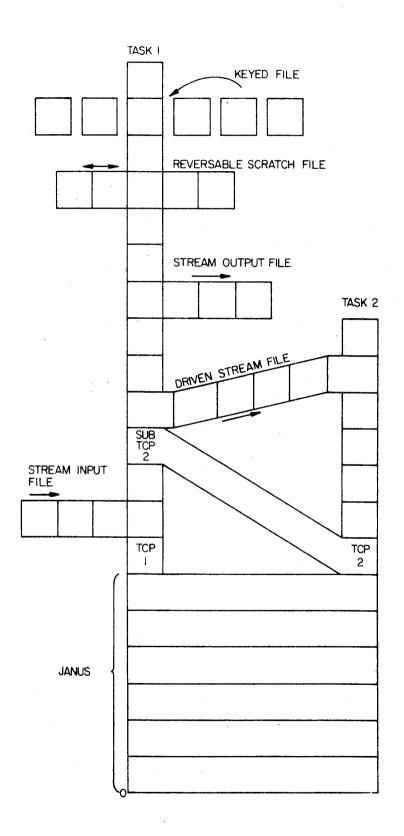

| 18. | Examples of address space usage, including files. The vertical columns are independent task address spaces, resting on the JANUS block common to all tasks. Two tasks are shown, with TASK 2 being a subtask of TASK 1. The two tasks have one page in common (TCP 2) which appears in different parts of the two task address spaces. The two tasks share a driven stream file, which is also referenced from different parts of the two address spaces. It differs from the TCP 2 usage, however, in that file driver (TASK 1) may be several pages ahead of the file receiver (TASK 2). The files are a collection of diskpages, each of which may be used as the same address space page. Only one page of a file is actually within the task address space at any given time, however. Files may be linked internally, or may be linked through a table residing within the task, as is shown in the keyed |   |     |

|     | file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | • | 62  |

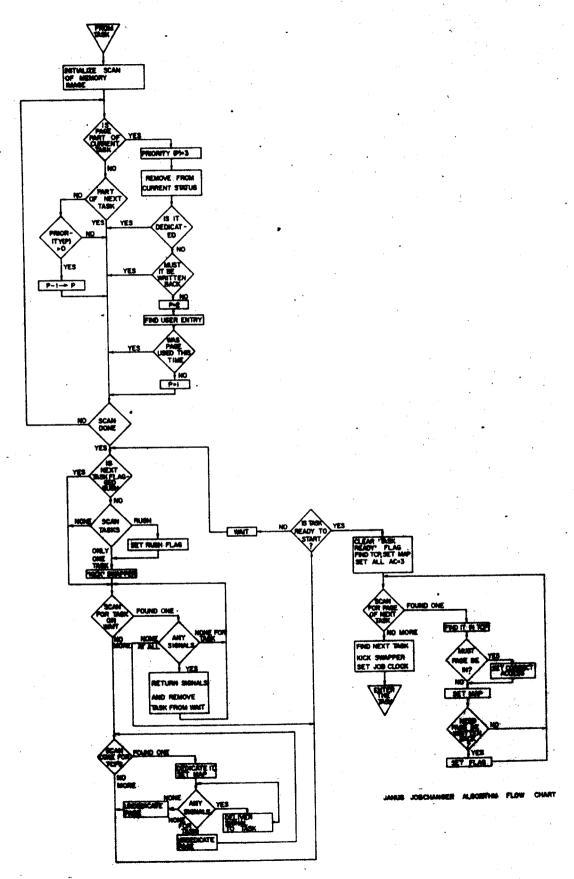

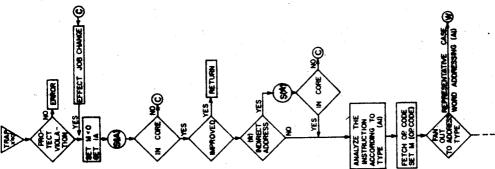

| 19. | The Job Changer - flow chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • | 92  |

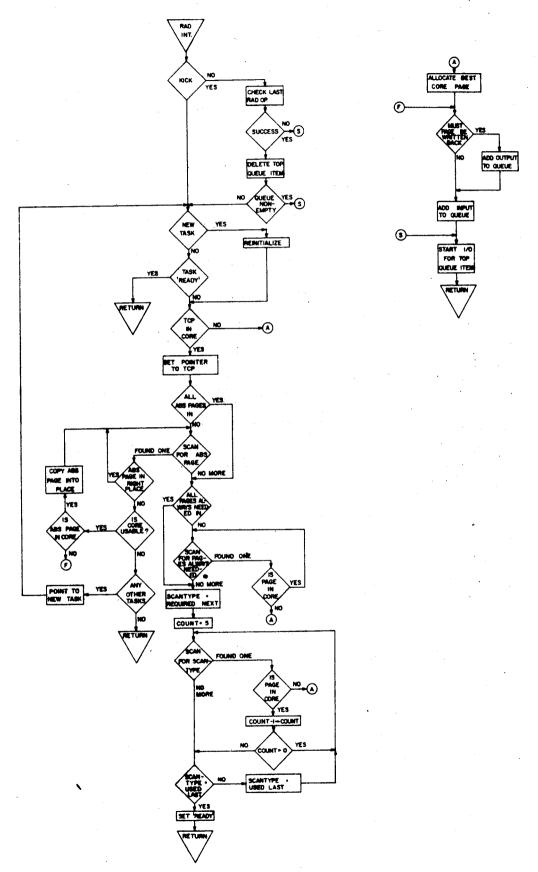

| 20. | The Swapper - flow chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • | 98  |

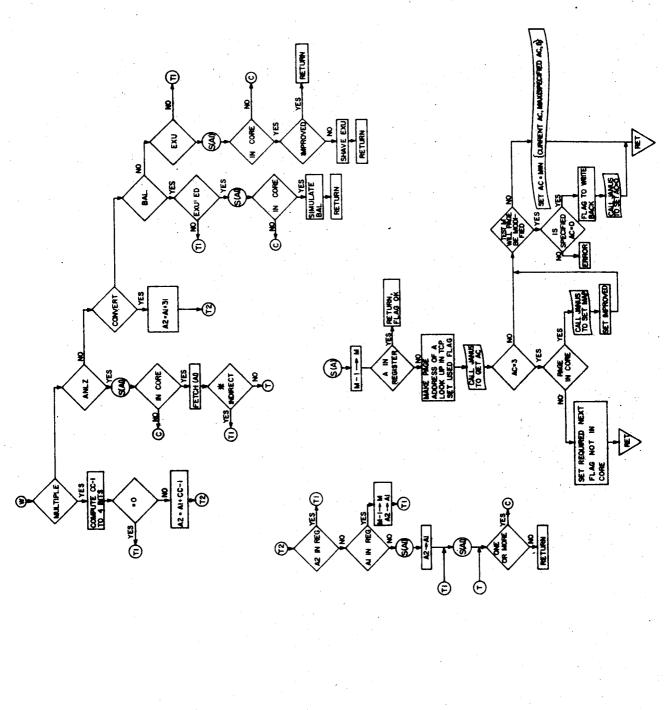

| 21. | Demand paging - flow chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • | 107 |

#### 1. INTRODUCTION

Physicists have used digital computers for as long as computers have existed. Indeed, long before the first computer was built physicists were suggesting that computing machines would be useful for generating astronomical and mathematical tables. More recently, with the advent of quantum mechanics, people such as Hartree called for the development of machines to perform computations for the calculation of wavefunctions and energy levels of atomic structures.

As soon as electronic digital computers became available, they were set the task of performing physical calculations. The usage of computers took great strides with the successive introduction of assemblers (which freed the programmer from the nuisance of bookkeeping relevant to the computer but not to the operation he wished to perform), and compilers (which permitted the programmer to forget all details of a specific computer, but instead to write programs usable on all computers which had a similar compiler available). The earliest languages (FORTRAN, ALGOL) were developed as aids to computation. Their success lead to the development of larger and faster computers. This in turn permitted the development of more powerful programs, which led to concepts of batch processing.

Batch processing was a logical development of the observation that, over reasonably long periods of time, the computer averages as much time spent reading cards and printing as it does computing. Since the bulk of the operations involved were read, print and punch, the computer

could obviously do more computation if these operations could be done faster. However, there are limitations to how fast a device may be operated. Further, these operations could be performed by a timy computer. Thus multiple computer systems were developed, where a small computer cepied cards onto magnetic tape which was later read by the large computer at much higher speed. The large computer then would write the output on other magnetic tapes to be printed later by the small computer. This provided improved usage of the large computer, and the value of the additional computation more than offset the cost of the additional small computer. However, since the computer now performed all operations automatically, it was no longer possible for the programmer to know just when his problem was being processed, and to interact with it. Furthermore, a fairly long time delay was required between submission of a problem and the return of the results.

People soon discovered that the small computers were useful in their own right, and that for many simple problems, results could be returned faster than with the large batch processing systems, since almost no computation was required. Thus a continuing development of small computers paralleled the development of the large computer systems.

With the rise in computer technology, it became possible to build special purpose computers, usually consisting of a hard-wired program and a memory. In nuclear physics, these were best typified by multichannel and later multiparameter analysers. While extremely useful, the allowed sequences of operations were built into the machine and were relatively inflexible, being limited to specific configurations which could be changed only with great difficulty if at all. It was usually necessary to do complex operations external to the analyser. Further, it was

not possible to manipulate the data once taken, but only to dump it onto a secondary storage medium.

As computer technology improved, small computers became more powerful and less expensive. By the early 1960's, it became both feasible and desirable to attempt to interface a small digital computer to a nuclear physics experiment 1). This was successful, and proved to be much more flexible than a hard-wired analyzer. Similar systems began to spring up in many places. As programs were written and used, it became apparent that the main value of a computer attached to an experiment lay not in its flexibility as an analyser, but rather in its use in an interactive mode with the experimenter. For the first time it became possible for the experimenter to provide flexible and elaborate checks on the experiment, such that the computer could inform the experimenter of questionable operation or malfunction, or provide, on demand, a list of parameters which would aid him in determining the status of the experiment. Further, it became possible to analyse data as soon as it was collected, and compare the experimental results with theory. Parameters could be varied in both the theoretical calculations and the experiment, allowing more accurate measurements of the quantities of interest. There was a definite possibility that an experiment would proceed faster, since it might be possible at an early state to determine that the effect of varying one parameter was negligible, and could be ignored. Data analysis could be completed with the experiment, and questionable data could be retaken if necessary while the experimental configuration was still operative.

There was, however, one serious drawback to this system. The computer was dedicated exclusively to the use of only one person at a time.

The period involved might cover days or weeks, during which time no other person could use the computer. Since the experimentalists normally discovered a few days after their experiment that they would like to wary another parameter with respect to the data they had collected, since they already knew how to operate one computer, and since they knew that they could analyze their data under an interactive system much faster than by sending it to a computation center for batch processing, computer usage became saturated. A struggle invariably developed between the person who was using the computer and those who wished to use it for data analysis, data reduction, simple computation, and development of new programs to make use of the computer. Each time a new program was developed and added to the library of useful programs, saturation increased. Furthermore, it was apparent that the computer was not being used at full efficiency, since programs rarely used all of the resources of the computer, and for long periods various resources could be seen standing idle. Two or more people who required non-overlapping resource subsets could easily share the computer, if a mechanism suitable for sharing were provided. Then "A" could analize his data using a graphic display and teletype, "B" could be reading cards and printing out the results of a computation based thereupon, while "C" could copy a magnetic tape.

Such a mechanism exists, namely timesharing, based on the observation that if in an interactive mode of operation, a computer is normally

idle while waiting for a person to respond, then during this time it

could easily be responding to each of several users, without appreciable

degradation of response to any one. As a result, each user would feel

that the computer is devoted exclusively to his use. The computer could

still be providing a batch processing facility in the background of its

operation, or any other processing which was not time dependent. This background usage would be degraded by the interactive usage, but would still be keeping the computer busy and productive.

Timesharing schemes fall generally into three categories. These may be classified as follows:

- 1. Systems where all users are running independently, but where each is performing identical operations of computation, control, and input. Such a system would use the same program for all users, each differing only in the unique storage area he was using. In this scheme, the program is reentrant, such that it always assumes one or more pointers to the current area of storage it is manipulating. This scheme is effective where each terminal that may interact with the computer is identical in its capabilities and operation. Added flexibility may be provided by allowing the individual user to use his own programs, executing them from his storage area, to manipulate his data. However, any interaction between the user and his program must be handled by the main resident program, or monitor. Further, all allowed functions must be built into the monitor, and adding or changing a function is a nontrivial programming problem. A common example of such a timesharing system is that used by airlines for ticket reservations. Such a scheme is relatively easy to produce, since there is a finite set of operations allowed and desired. Its greatest deficiency lies in its lack of flexibility.

- 2. A second scheme is that of foreground-background usage, shown in Figure 1. Here an area of the memory is set aside for one or more foreground programs, which interrupt the program operating in the background as necessary to perform a specific set of functions and return

Figure 1. Memory allocation under a foreground-background scheme of timesharing. The vertical column represents core memory. The monitor is used to provide all control functions. The area of core devoted to background timesharing is successively occupied by a number of processes, all limited to the size of the background area. The realtime foreground area may be occupied by any one of a set of processes, (or divided so that it may be used by more than one process), but any realtime process generally locks out all other realtime processes.

CONVENTIONAL TIMESHARING WITH REALTIME control to the background when done. Usually there is a method of checkpointing the current background program, that is, saving it on an external storage medium, replacing it with an extension of the foreground program capable of performing certain complex operations, and when there is no longer any need for this, restoring the background program and continuing its operation from the point it was checkpointed. However, there is normally elaborate checking involved to insure that the foreground and background programs do not interact, as there would be great dissatisfaction on the part of the users if it was necessary, for example, to sort output because the foreground and background punched alternate cards or printed alternate lines. The big advantage of the foreground scheme is that of fast response to events, thus permitting evaluation of each event on its own merits. The disadvantage lies in the difficulty of changing the foreground. In a situation where the foreground is used to monitor and control a process, such as the operation of a manufacturing complex (eg. oil refinery) or complex machine (eg. accelerator), where parameters may be varied but where the foreground program is rarely changed, this is no real disadvantage. However, in a situation where multiple foreground operations may be in operation simultaneously, starting and stopping asynchronously with each other, severe problems occur with respect to keeping track of free memory and making efficient use of the memory.

3. In the third scheme each user is performing operations completely independent of all other usage of the machine. This scheme, while being capable of the greatest degree of flexibility, is normally found to be so difficult to implement that restrictions are placed upon all usage. For example, no user is permitted to change the state of the

machine himself, and must request all state changes from the resident monitor. This monitor must on each request, determine if the request is valid, if the operation is permitted to the user, and perform other bookkeeping functions before actually going ahead and performing the operation. A typical operating system could easily require 20,000-40,000 words of memory at all times just for the resident programs. In addition, response time may be increased drastically such that, while still adequate for response to people, the response time is orders of magnitude slower than would be possible in a foreground system. This would seriously limit the usefulness of the system in an environment where events could occur thousands of times per second, such as in a nuclear physics laboratory.

This thesis describes a new scheme of realtime timesharing, which, while permitting the flexibility of scheme 3 above, also permits the response time associated with foreground programs, without many of the disadvantages of either scheme. It has the further advantage that the requirements of a resident monitor are kept to a minimum, since the task associated with each user performs all of his monitor functions, including all communication with the external world (IMPUT/OUTPUT or I/O). This is shown in Figure 2. This is of great advantage in nuclear physics experiments, where an I/O operation might require a buffer of thousands of words, wasteful to make resident unless used frequently enough to justify it. (The acquiring of a multichannel or multiparameter spectrum can be thought of as such an I/O operation, where the storage allocated to the spectrum is in effect a single buffer.)

The operating system described is called JANUS, for the Roman god w...of all going out and coming in,...also the god of entrance into a new division of time 2, thus the god of timesharing.

Figure 2. Memory allocation under JANUS. As in Figure 1, the column represents core memory, with JANUS at the bottom. Two tasks are shown, with the independent task address spaces twining through memory. Not all pages of a task need be in core at one time. The darkened pages of core are dedicated to realtime processes specific to the task which has the page.

STYLIZED REPRESENTATION OF MEMORY USAGE UNDER JANUS

Figure 2.

#### 2. THE USE OF CORE MEMORY

In order to provide a perspective for the discussion of JANUS, I will first describe how various other timesharing systems operate. Consider first the problem of sharing the core memory of the computer. How can more than one user make use of the core memory without the possibility that an error can interfere with another user? (Subsequent figures are keyed to Figure 3.)

The simplest scheme is to have only one user in core at a time, and all available core is his to use. This scheme is that used in Project MAC of the Massachusetts Institute of Technology on an IBM 7090 computer (Figure 4). It is also used in the Sigma 7 timesharing system developed by the Bubble Chamber Group at Brookhaven National Laboratory 3). The users program is brought into core from an external storage medium (swapped), and started. If the program did not inform the resident executive program that it wished to exit early, then at the end of a fixed time increment execution is stopped, the current status is saved, and the program is swapped out to the external storage medium, freeing the core for the next user. This process continues for each user, until eventually the first user is swapped back into core, and his execution is continued. While this scheme has the advantage of simplicity, the amount of time spent on nonproductive bookkeeping (overhead) is high, as the computer is idle while swapping occurs. To provide a reasonable response time to each user, the interval specified (timeslice or time

Figure 3. Key to subsequent figures. (Note the use of the word active, which in this context refers to a task executing a timeslice.)

Figure 4. Memory allocation--project MAC. User execution alternates with swapping (the process where the program is transferred to or from memory).

Figure 4.

,

quantum) must be short—normally fractions of a second to each user. An example of the problems involved for such a scheme is demonstrated in the Brookhaven system, where the average time required to replace one block of 8192 words with another is 56 milliseconds. With the 1 second timeslice used, this provides 5.6% overhead, but with 6 active terminals as much as 5 seconds may pass before the computer can respond to the user. Three second response time is normally considered a reasonable upper limit. To provide this response time, a time slice of .5 seconds would have to be used, and overhead would increase to 78 milliseconds. Most terminal usage consists of the computer reading in a typed record, examining it, possibly commenting upon an error, and requesting new input, a process which normally takes much less than 1 second. In this case, the overhead would increase to a large value. Inter-user protection need not be considered, however, since they cannot get at each other.

By constraining each user to a separate part of the core available, such that more than one user may fit into the core memory, advantage may be taken of the fact that most computers suitable for timesharing are capable of asynchronous I/O operations, such that I/O may coexist with program execution. Thus one user may be executing while another is swapping in or out. The swapping I/O overhead is negligible as long as the timeslice is greater than or equal to the swapping time. However, a new problem arises—that of relocation. To make efficient use of the memory, a program should be capable of executing correctly wherever it may be located. Unfortunately, programs tend to reference absolute addresses.

The simplist method of treating relocation is to ignore the problem. This approach was taken by Dartmouth College with a GE 265 4) (and more recently a GE 415) computer (Figure 5). Available core is divided into two areas, "high" and "low" core. Execution is alternated between high and low core..as low core is executing, high core is undergoing a swap. However, a program loaded into high core will not run in low core, and vice versa. A bad job mix can cause an excess of programs in one area or the other, with the result that either the low density area users get more computer time, or else the computer becomes inefficient, as time must be spent waiting for swap in the high density area. Additionally, any system library program which is available to all users must be kept in both a high and low version. Protection is provided by a bound register, which specifies the highest and lowest legal core references permitted.

In order to treat relocation adequately, so that a program may run in different areas of core without revision, special hardware must be used; if the relocation operations were performed by software the overhead would be tremendous.

There are three methods of automatic relocation used. Two of these are almost identical, with only a slight difference in emphasis.

The first of these methods uses a location register and relative addressing. Each address is relative to the referencing instruction. The actual reference is made by adding the location register to the address specified. The block of code will now operate anywhere in core automatically. This scheme has been most successfully applied to the SDS Sigma 2, which is not however used for timesharing.

A second scheme uses a base register. Addresses specified are relative to the beginning of the program, rather than to the address of the instruction; otherwise operation is identical to that outlined above.

Figure 5. Memory allocation--Dartmouth project. A new program is swapped into core memory while the current program is executing. However, an imbalance in the number of jobs assigned to high and low storage causes a delay at the end of the third timeslice, as there is nothing to do but wait between USER 3 and USER 1.

Pigure 5.

This scheme is used on the IBM 360 computers (5, 6), and in the PDP-6 7) (and now in the PDP-10) computers (Figure 6). There are two advantages of this scheme over the Dartmouth scheme. First, successive users are placed where there is room in core, without the problems associated with high and low core areas. Secondly, programs may be of variable length, up to half the available space in extent. Short programs can coexist with longer programs. This scheme further introduces the concept of pages—a basic unit of core size. In the PDP-10 each program consists of an integral multiple of 1024 word pages. Protection is again provided by a bound register, the lower limit of which is also the base register.

The third scheme of auto-relocation involves a memory map. First developed by Project GENIE at the University of California, Berkeley, using an SDS 940 computer, it is also used by the IBM 360-67 (8, 9), and JANUS in an SDS Sigma 7. Figure 7 shows the use in an SDS 940 computer, which uses 2048 word pages. Note that pages which are modified (M) while a program is active are flagged to be written back (W). Since for unmodified pages there is a true copy on the external storage medium, these pages are preferentially chosen to be overwritten thereby cutting down the number of swap operations necessary. The penalty for reducing the number of swap operations is the necessity of searching through a table of content-associated core pages, to determine if a page of a program is currently in core. Programs execute in a virtual address space, connected to the real address space of the core memory through the map. Thus contiguous virtual pages need not be in contiguous real pages of core, but may instead by located wherever most desirable. Inter-user protection is afforded by a multilevel page protection system, used to

Figure 6. Memory allocation--PDP-6 computer. Swapping occurs concurrently with execution, but the efficiency is higher than in Figure 5, as no limitation is imposed by the use of specific areas. Note that a significant part of memory is rarely or never used.

Pigare 6.

Figure 7. Memory allocation—project GENIE. Problems are initially brought into free core. When no more core is free (TASK 4), those pages are chosen which are not currently in use and are identical to the copy on the disk (unmodified), to be overwritten by new pages. The resultant fragmentation of jobs is offset by the use of a memory map. Not until the sixth timeslice is it necessary to write a page out to the disk (TASK 1, Page 5). This scheme is also used in JANUS. (The P numbers are pages within each user's address space. M signifies that the page is modified, W indicates that it must be written back onto the disk.)

Figure 7.

protect and monitor the usage of pages.

Under a mapped paging scheme, the usage of each page may be closely monitored—closely enough, in fact, to permit demand paging. If the executive system can be informed whenever a page is referenced, and if the user can be locked out of some of his own pages, there is no longer any need of the whole program being in core. Those pages currently being used can be brought in, and if a valid reference is made to a page which is not present (demanded), the current timeslice can be stopped, and conditions set up such that the demanded page will be available during the next timeslice for the program. Further, if a page is not referenced for some period of time, it may be safe to assume that it will not be referenced again for a while, and eased out of core memory in order to make room for pages in use.

Vantage over that specified above. Much of the executive is unique to the task, rather than resident and common to all tasks. As a result, it is entirely up to each task if demand paging is to be used. Turthermore, any task's monitor may dedicate one or more pages, making that area resident until undedicated (Figure 8). These portions may be connected to interrupts, permitting realtime operations asynchronous to timesharing. These pages form resident islands, and timeshared usage maps around them. All the advantages of foreground usage result, without the rigidity inherent in conventional foreground-background systems. The added ability to solve problems which are actually larger than physical core, without requiring special techniques of the programmer, such as overlays, is a boon.

Figure 8. Gross memory allocation under JANUS, showing realtime processes. Using a large time scale, all short-term details of memory usage are omitted. Shown instead are areas dedicated for realtime processes. The blank area is available for swapping. The activation of four tasks is shown, each of which immediately initiates a realtime data input process. These tasks, in order of appearance, might be MOIRAE, JBCM, DATA TAKER, and JFCM. Note the interleaving of lineprinter output of tasks 1 and 2. The variable size scope display is a measure of the amount of realtime buffer area required as a display is expanded to show relationships instead of detail.

Figure 8.

# 3. BULK STORAGE

Almost all time iting schemes require, in addition to the core mamory, additional bulk storage to keep programs, libraries, and data. In general, this storage is addressable, in that a specific block of storage may be located without searching all the storage medium. With certain exceptions, magnetic tape does not fall into this category. Instead, magnetic tape is a serial or "stream" storage medium, where records relative to the current record may be referenced. As such, it is useful primarily as an archival storage medium, where data stored thereon is not capable of change without either destroying all succeeding records or requiring a copy operation to move the data from a source tape to a destination tape, making changes as necessary in the new copy. This use is adequate for storing data, and for some functions such as holding lineprinter output. It is inadequate for working bulk storage in a timesharing environment where response time is critical.

In this environment, addressable storage is required. Commonly used storage takes many forms, some of which are indicated in Figure 9. Shown also is the typical access time and range of storage capability for that form of storage, as well as cost. Cost and storage are in terms of bytes, a byte containing 8 bits of data. It is readily apparent that as access time decreases the cost increases. This factor of cost/byte is what normally sets an upper limit to the practical storage capability for a particular form of storage.

Figure 9. Characteristics of various bulk storage media.

Timesharing systems require an immense amount of bulk storage, normally approaching infinity as closely as possible. In addition, it is normally desired that access time be as low as possible. To be practical in terms of cost, it becomes necessary to build a bulk storage structure, using a set of storage forms of differing characteristics. Thus, one uses a fast, low volume medium as well as a slow, large volume medium.

This storage structure may take three possible forms, of which the linear form is rarely used in comparison with hierarchical and hybrid structures, at least for timesharing usage.

The most easily understood structure, however, is the linear structure, shown in Figure 10. Here the storage is an extension of the core memory, but suffers from the difficulty and inconvenience of executing programs directly from the storage. Its advantage lies in the fact that there is a unique address associated with every piece of storage, both core and bulk. Operation consists of copying blocks of data into core memory, manipulating them, and then replacing them.

The opposite extreme is the hierarchical or pyramid structure (Figure 11). In this scheme, unused sets of data are kept at the lowest (large capacity, slow accessibility) level of storage. If referenced, the set of data is brought into core, and, if necessary, later written back. The system executive does automatic accounting of usage—if a data set is used frequently enough, such that time spent accessing a level of storage becomes significant because of frequent references, that data set is copied through core to the next higher level of storage.

Depending on the algorithm used, the original block of storage may or may not be freed (depending on whether or not the storage is referenced

# NON-EXECUTABLE BULK STORAGE CORE MEMORY

Figure 10. Linear bulk storage structure. (Used by CDC 6600 (extended core storage) to hold programs and non-executable I/O buffers.)

FILE ADDRESS SPACE ----

Figure 11. Hierarchical storage structure. Access time decreases with height. Each storage medium has an independent address space. by a unique name, or by its areal name on the lewest level). As the use of this procedure unaided would tend to fill higher levels of storage, a mechanism must be provided to purge a level of some data sets, whose usage frequency does not warrant such a high level of storage, to a lower level. This may be done periodically, as well as upon demand. Efficient use is made of bulk storage, but there are two disadvantages to such a scheme. For ease of description, I will assume a data set consists of a group of pages, and consider the use of a single page.

First, and most important, a page must be referenced by a unique name. This name will have associated with it indicators telling the current level and location within that level of the specific page, as well as some sort of usage indicator. A table is required to permit the association to be made. In addition, some indication must be provided for free pages on each level, as well as for free names. In order to provide speed of reference, at least part of this table must be resident. Since a minimum of one word/page is indicated, and since storage of 100,000,000 bytes (50,000 pages) may be available, it is readily apparent that an excessive amount of core storage is required for the table. There are alternatives, requiring only a list of the contents of the highest level of storage, but these are expensive also, as each reference requires searching the table to see if the reference is there—a time consuming operation.

Secondly, the overhead introduced in purging levels is non-trivial.

A typical hierarchically organized system is the IBM 360 Time

Sharing System (TSS) (8, 9). Using a complex algorithm to improve efficiency, measured overhead is still 80-90% 7).

The third form of storage structure (Figure 12) is the hybrid

structure. In this scheme, all names are absolute rather than relocatable, and no resident table is required, except for a list of unused pages for each storage medium, and an associative table of the pages contained in core memory. Pages are allocated according to expected use and duration of existence--program libraries in slow storage, active programs in fast storage. If a storage medium is full, space is allocated from a slower medium. A program is copied to fast working storage and remamed when it is brought active, and that area is freed when it exits. As a result, little overhead is required compared with the hierarchical structure, and the benefits of the linear structure apply, without the problems associated with nonexecutable storage.

JANUS uses a hybrid storage structure. As the MSU Sigma 7 configuration includes only a single bulk storage medium (a 1.5 megabyte H/T disk), it is a simple structure. However, only a relatively minor change in JANUS is required to implement one or more additional storage media.

# 4. SCHEDULING OF TIME

In any timesharing scheme, the timesharing is effected by dividing the time available into quanta, or timeslices, which are allocated to successive users. Scheduling involves two parameters—timeslice duration, and ordering of users.

Timeslice duration may be fixed or variable, and a mechanism is usually provided to terminate a timeslice early. A fixed timeslice has obvious meaning; each user gets the same quantum of time for his problem.

A variable timeslice is normally used in a timesharing system where the status of the machine, the system, and the previous history of a particular task's usage is available. On the basis of these parameters (and possibly others, which may be defined by the user), an "optimum" timeslice is calculated for each user each time. Thus, if the machine and system are lightly loaded, a longer duration is provided than if a heavy lead exists such that many users must be serviced within a given period of time. Again, in a priority oriented system (see below), the duration is related (perhaps proportional) to the amount of time a user's problem has already taken. The rationals for this scheme is that, if a problem has already taken a certain period of time, a longer timeslice alloted to it will cut down on time spent for system overhead, and more productive work will be accomplished. For example, a problem which has already required H timeslices of duration T may be

given a duration of 2T for the next N timeslices. If still not done, the duration might rise to 4T for the next 2N timeslices. Since an extremely long calculation, such as frequently arises in scientific work, might require hours of computer time, a mechanism must be provided to permit the abortion of a long timeslice, in order to allow access to the machine by other users.

A further perturbing factor may be the admission of a user to specify his own timesharing, as in tasking under PL/1 <sup>10)</sup>. In this case, a user may start subtasks to operate concurrently with the controlling task, and specify what portion of the time the computer is to spend on each. Then the duration allotted to the user must be divided into appropriate sub-quanta to permit each of his tasks its proper allowance of time.

The second phase of scheduling involves ordering the access of a user to the machine. The simplest ordering is to place all users into a "ring". In a simple ring, all users, both active and inactive, are in a circular structure. Control passes from user to user sequentially, skipping these who are inactive. Users may pass from active to inactive states and vice versa. The access time for a user then depends on his position in the ring relative to the currently active user. (A user is active if his program can proceed with computation, rather than wait, as for example for input.)

A more sophisticated approach is to have a ring of active users.

and a list of inactive users. When a user is activated (goes from the inactive state to the active state), his task is inserted into the ring as the next task to run. This has the advantage that an activated user task has a short access time, and therefore fast response time. If

the task stays active for longer than a timeslice, he enters the normal ring sequence.

An extension of this scheme is the assignment of priorities to the tasks (the above is a two-level priority scheme). A multilevel priority system is generally an aristocratic system: all tasks at a given level are exhausted before proceeding to a lower level. If a level is being executed, and a task appears on a higher level, the lower level processing is discontinued. A task activated is normally entered into a high level.

Under priority scheduling, there may be a pyramid of rings (Figure 13). These rings leak--if a task stays active for long enough, it drops to a lower priority level. If it goes inactive, it drops to the lowest (inactive) level. As described above, lower priority tasks may be given a longer time quantum, to offset the fact that they may be entered less often.

In general, the parameters used to define priorities and timeslice duration are produced by an empirical fitting process, based upon

some specific mix of possible jobs. In a terminal-oriented timesharing

system, a .1 second quantum may be used for the highest priority, to

provide fast terminal response time, and may expand to several seconds

at a lower level, where long computations are performed.

JAMUS uses a scheduling algorithm with a two-valued timeslice and a four-valued priority scheme. A task is allocated a .1 second timeslice, unless it is the only active task in the machine, in which case it is alloted .4 seconds. If a realtime process requires rapid response from its associated task, it can bring the task active, and even effect jobchange for the currently active task.

Figure 13. Priority scheduling. A task in a high priority ring will be accessed more rapidly than one

The possible priorities are inactive, normal, hurry, and rush, in order of increasing level. The structure is that of a simple ring—an activated task remains in its normal sequence. However, a task may be placed in a higher priority level than normal. The use of a higher priority everrides the normal sequence of operation, and the first high priority task encountered is used.

The difference between hurry and rush priority is one of efficiency, Under rush priority, a task is made ready and started, even if another task is ready to proceed. Under hurry priority, if another task is ready to proceed, it does so, rather than have the computer wait while the high priority task is readied. A task found in either high priority state is reduced to normal priority on entry; thus high priority applies only to the first access. On return from a high priority task, execution will proceed with the next task in normal sequence from it, unless another high priority situation exists.

Since JANUS is a system geared to realtime operations, there is a second form of timesharing available. This is by means of interrupts (Figure 14). A realtime event may be defined as the occurrence of an event asynchronously with the operation of the computer. If the event is attached to a hardware interrupt, it is possible to rapidly switch the complete state of the computer, interrupting the current process, and transferring control to an interrupt routine. This routine may take the necessary action based upon the event, and then return control to the interrupted process. While the interrupt is active, it can have performed various operations, including the activation of the associated task. In general, all I/O operations are associated with interrupts, including data acquisition. Indeed, the basic JANUS functions ef

Figure 14. "Timesharing" by interrupts. Execution alternates between the background (lower) and foreground (upper) line, on the basis of interrupts. While a simple case is shown, interrupts need not all belong to the same foreground process. "Timesharing" by interrupts. Execution alternates between the background (lower) and

swapping and jobchanging are associated with interrupts, although of lower priority than those used for data acquisition.

Realtime processes operate in the foreground of the computer—timeshared operations in the background. As a result, it is possible to perform a nuclear physics experiment at several levels simultaneously, such as realtime data acquisition, realtime I/O (e.g., plotting), realtime timeshared data analysis, and timeshared theoretical computation.

Each of these can be treated as an independent process, and thus the processes necessary to a particular experiment may be selected and started. If it is discovered that an additional process is required during the course of an experiment, it may be selected and added to the set of active processes. Similarly, a process no longer required may be dropped.

# 5. DESIGN GOALS OF JANUS

JANUS was first designed to optimize realtime processes, specifically data collection, control, and interactive processes relating to experimental nuclear physics. Only after it was decided that these were the most important functions of the computer for our application, was an attempt made to determine how to proceed 11). An analysis of projected usage indicated that any realtime process had associated with it a large body of associated data and program which was not used continuously, and which was of low priority. Also indicated was the fact that, while a realtime process was active, large portions of the computer resources would be standing idle. Furthermore, the capability of operating multiple independent realtime processes simultaneously was desired.

It rapidly became apparent that a timesharing system was desired, with a capacility of running realtime processes in the foreground, while the associated programs (and independent ones also) would run in the background. Efficient use of core memory indicated the need for a small resident monitor, as well as memory mapping. Tasks were defined, and their requirements and capabilities were delineated.

The result was the JANUS philosophy:

1. The highest priority use of the computer is to service interrupts, and external data collection associated interrupts should be of highest priority. There should be no critical timing requirements on any sequence of code, requiring the inhibiting of interrupts.

- 2. Any hardware in a given installation should be available to a user if he needs it.

- 3. The only restriction on any user should be that all other users are protected from him, as he is from them.

- 4. No user should be aware of any other use of the machine, except when a delay is required because of a request for a currently unavailable resource.

- 5. It is the responsibility of the task associated with a user to insure proper operation, as JANUS is to impose no arbitrary restrictions by checking on the task. JANUS should be invoked only for control functions.

- 6. What a user does not know about the system should not hurt him, as long as he follows reasonable conventions as to usage.

- 7. A user need not have any knowledge of anything he doesn't use, to the extent that it does not exist in the machine he is using.

These goals have been met in JANUS.

# 6. UNIQUE FEATURES OF JANUS

The system is based on the observation that a piece of a program need only be accessible while it is being referenced. In a timesharing system, programs succeed each other at small intervals of time. The only piece of any such program which need be in core at all times is that piece which may be called upon asynchronously to the normal sequence of timesharing. It is readily seen that this description is exactly that of realtime operations, which can be extended to include all forms of I/O. If a mechanism is provided for a task to make a part of itself resident for the duration of a realtime requirement, then it becomes feasible to timeshare monitor systems, since, in general, monitors provide primarily for realtime I/O functions and any operations or usage which it is not desirable to allow to the user directly.

Further, if a mechanism exists to determine the usage of a block of storage including its accessibility, then the only blocks which must be available each time the task is active are those blocks to which the mechanism does not apply. Other blocks meed not be accessible, or even in core, if a mechanism is provided for fetching them as necessary.

Again, if a mechanism exists for automatic relocation, such that a given piece of program can be operated successfully from different parts of the real computer memory, then these mechanisms can be used as a memory expander, such that programs can operate anywhere in the address space (chapter 9) of the computer whether or not that address space

corresponds in full to existing memory.

Furthermore, each task may operate in a completely independent address space, or several tasks may intersect in one or more blocks, which need not, however, correspond to the same piece of address space in each of the intersecting tasks.

In order to describe how these mechanisms are implemented in JANUS, it will first be necessary to describe unique features of the target machine, a SDS Sigms 7 computer. Certain features of JANUS have been influenced greatly by the operations allowed by the hardware. Some of the operations necessary to JANUS are provided quickly and easily by the hardware, showing the power and utility of such hardware, while others equally important must be implemented in a less than straight-forward manner, and would benefit greatly from the existence of hardware suited to the application.

### 7. THE TARGET COMPUTER

The SDS Sigma 7 computer 12) is a relatively new third generation computer of which MSU acquired the first sold. A first generation computer is generally typified as consisting of some form of memory and a processor, which can acquire specific data words (instructions) from the memory and based upon these instructions manipulate other data words. This generation usually used vacuum tubes. Second generation computers are typified by the use of transistors, and include such features as index registers, I/O channels (a device which shares the memory of the computer, and which, on command, can perform asynchronous operations for the computer, such as transmitting a whole string of data elements, rather than just one), and interrupts, allowing multiple use of the computer. The third generation computer is distinguished by the use of integrated circuits, and features such as privileged instructions, paged memory, memory mapping, flexible memory protection, "scratch pad" registers, and I/O processors. These are discussed in turn below.

Privileged instructions: the computer may be operated in either slave (computational) or master (control) modes. In slave mode, all instructions relating to the internal use of the computer are permitted, but certain control instructions are illegal, and memory usage is controlled. Conversely, in master mode, both internal and privileged control instructions are permitted, including those which change the status of the machine, but the core monitoring capability is lost.

A paged memory means that a natural unit of memory exists, such that specific conditions may be applied to one page and not another. In the Sigma 7, the size of a page is 512 words. These pages are indistinguishable in their usage except for the real memory sequence they are in, with special usage for the first page in this sequence (page zero).

Memory mapping is special purpose hardware to provide automatic relocation by pages. Associated with this is a table, the map, which specifies the usage to provide. Under this scheme, each page of memory is automatically, and with insignificant cost in time, mapped into a specific real page of memory. There is no requirement of identity, and thus the address space the computer is operating under need have no correspondance with space in the real memory, except in special cases. As a result, a task may be loaded by pages in such a way that the most efficient use is made of the existing memory, independent of the address space requirements of the task. There may be a one-to-one correspondance in regions of the map, as an alternate device to the pointers described in timesharing scheme 1 in the introduction.

Memory protection is that ability to specify the usage of certain pages of memory under specific conditions. For example, in the Sigma 7 operating in mapped slave mode, four modes of usage may be specified for each page, corresponding to the degree of access allowed. These access protects are: 0. Complete access allowed, 1. Write prohibited,

2. Write and execution prohibited, 3. All reference prohibited.

While intended primarily as an aid in debugging and to provide security, the access protect may also be used to monitor the usage of memory.

Memory is divided into fast and slow portions. The fast portion, although strictly a storage medium, may be treated as a large set of

registers with identical capabilities. These "scratchpad" registers are normally treated as specific locations in memory, and thus all register-register operations are a natural extension of normal memory. Indeed, execution of the program may proceed from the registers. The net effect is that of a two address computer, where one address space is a small subset of the other.

There is usually one or more I/O processors (IOP). These are essentially the small computer, described in the introduction as the batch

processing system, built directly into the large computer, an IOP is more

powerful than a channel, in that it can provide simple operations, such

as collecting data sequentially from several places in memory and combining them into a single record, or transmitting multiple records between the memory and a device.

These features describe the Sigma 7, but there are others which are extremely powerful, although not unique to third generation computers. The most important such feature is the inclusion of hard-wired subroutines. (It is not generally realized that all floating point operations fall into this category.) Since the operation is hard-wired, it may proceed relatively fast. Hard-wired subroutines are usually expensive, and are normally recognized by being an optional feature on the computer. The simpler ones may, however, be standard. The map and protection described above fall into the category of a hard-wired subroutine.

Stacks: it is frequently desirable in a program to be able to save information temperarily in a push-down list or stack, wherein the last item entered is the first item removed. The major use of such a feature is to provide dynamic allocation of storage. If all temporary modifiable storage is used in a stack, less storage is required than if

all storage were entirely static, its use is optimized, and recursive routines (those which may call themselves) become easy to write.

Conversion: the Sigma 7 has instructions for conversion between any two number systems, provided that the two are related by a weighted-number system.

Byte string: four standard and one optional instructions permit the manipulation of strings of bytes (character), with operations such as move, compare, translate, and search. These permit powerful text editing facilities.

Floating point: optional. Including single and double precision, this is useful whenever accuracy is unimportant, or the range or numbers involved is unknown. Used in scientific calculation, where complex operations are performed.

Decimal: optional. All operations are guaranteed good to 31 decimal digits. Numbers are carried around as binary coded decimal quantities. Used primarily for business applications, where the operations are simple and quantity of operations is the criterion. (It must be remembered that all operations on a single number must include the time spent to translate the number to and from a character string, and this may be appreciable.)

There is also an instruction (interpret) which is relatively powerfull in juggling tables of non-numeric data, provided that they are of a

specific format.

In addition, the Sigma 7 provides variable data bases, such as byte (8-bit), halfword (2-byte), word (4-byte), and doubleword (8-byte), and independent instructions to manipulate these data bases. In conjunction with these, a base addressing scheme is provided, such that any

indexing operation is automatically at the resolution of the data base.

There is also a set of instructions, called immediate instructions, which reference the registers only, using the 20 bit address field of the instruction as a signed operand.

In general, the Sigma 7 is a well designed computer, with a power-ful instruction set, designed for the convenience of the programmer, rather than the engineer. However, it lacks a few features which would be very useful.

Specifically, I feel that there are two sets of instructions missing. These may be classified as "logical immediate" and "queuing".

Logical immediate instructions would be an addition to the immediate instruction group described above, to include AND immediate, OR immediate, and EXCLUSIVE-OR immediate. The addition would be of great value for non-numeric operations, as currently it is necessary to provide a mask in core, even if meeded only once. The queuing group would be harder to implement, since it would need to be a hard-wired subroutine. A complement to stacks, queues are cyclic stacks, of first-in-first-out nature, rather than first-in-last-out. However, it would seem no more difficult to implement queues than stacks.

Additional instructions which might be of use are list processing instructions, where a list and count are provided, and the list is scanned until some condition is satisfied.

As far as the Signa 7 hardware is concerned, there is one major failing. This can be traced to the expectation that the computer would be used with a centralized monitor. As a result, there are a number of items of machine status which cannot be read directly, but must be represented by an image in core memory. These include the map, access

pretect, and interrupt status. In a decentralized system, as under JANUS, it is not convenient to keep a centralized record of all interrupt status. As a result, while optional power failure interrupts are available for the Sigma 7, allowing the status of the machine to be saved if power is lost, it is impossible to save the status of the interrupts.